SCIENTIFIC ACHIEVEMENT

Researchers found that a stack of ultrathin materials, characterized in part at the Advanced Light Source (ALS), exhibits a phenomenon called negative capacitance, which reduces the voltage required for transistor operation.

SIGNIFICANCE AND IMPACT

The material is fully compatible with today’s silicon-based technology and is capable of reducing power consumption without sacrificing transistor size or performance.

High efficiency, low disruption

Microelectronics is expected to account for about 5% of total electricity production by 2030 thanks to ever-increasing demands for information processing. Maintaining progress will require a fundamental shift toward more efficient devices, with an emphasis on materials compatible with state-of-the-art silicon technology.

The phenomenon of negative capacitance represents one possible solution, promising to significantly reduce power consumption in electronic devices while fitting seamlessly into current semiconductor protocols. In this work, researchers took a key step toward integrating negative capacitance into advanced transistors, with support from various government and industrial groups including Samsung, Intel, SK hynix, Applied Materials, and DARPA.

Inside the gate

A transistor is essentially an on-off switch for the flow of current through a semiconductor, activated by a small voltage from a “gate” electrode. A thin insulating layer (the gate oxide) separates the semiconductor from the gate. Increasing the gate oxide’s ability to store charge (i.e., its capacitance) lowers the transistor’s operating voltage and thus reduces overall power consumption.

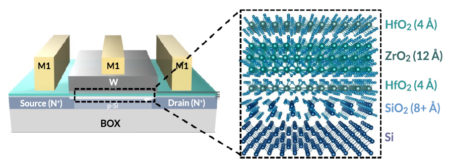

In advanced silicon transistors, the gate oxide is a combination of silicon oxide (SiO2) and hafnium oxide (HfO2). In this work, researchers replaced the HfO2 with a multilayered stack that displays negative capacitance—a counterintuitive effect in which decreasing the gate voltage increases the stored charge on the gate oxide, thus maintaining performance at reduced power.

Stabilizing negative capacitance

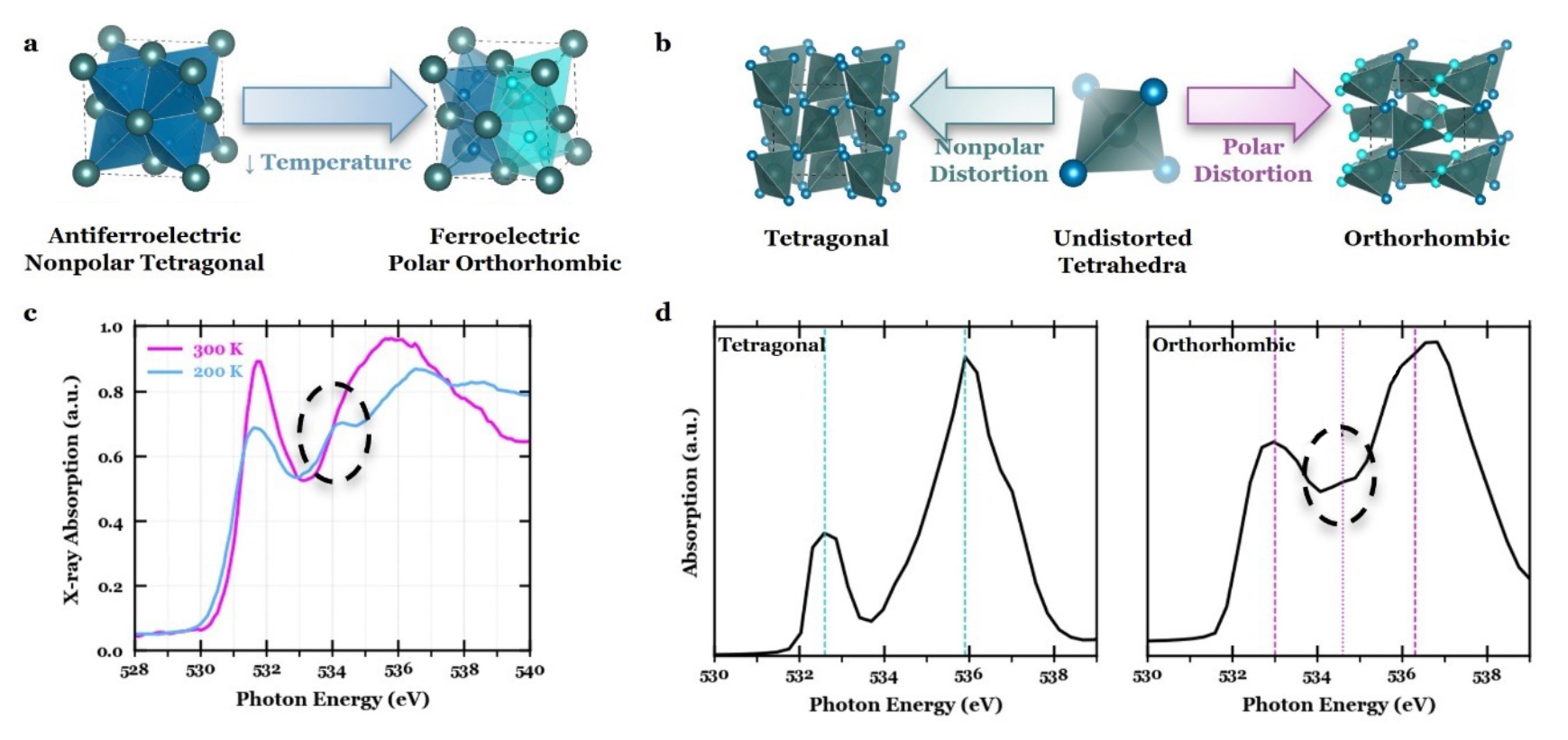

The creation of negative capacitance requires a material with some form of interacting internal order. Ferroelectric materials, for example, give rise to spontaneous electric dipoles—tiny charge separations arising from lattice distortions—that interact with one other. The negative capacitance effect can theoretically be strengthened by exploiting both ferroelectricity and antiferroelectricity.

To investigate this, the researchers synthesized a stack of three atomic layers of zirconium oxide (ZrO2) sandwiched between two single atomic layers of HfO2. This hafnium-zirconium-hafnium (HZH) heterostructure was predicted to have an energy well where negative capacitance is stabilized. Several synchrotron facilities—the Advanced Photon Source, Stanford Synchrotron Radiation Lightsource, and the ALS—provided valuable data about the structural changes that give rise to the ferroic order in this system. Advanced imaging at Berkeley Lab’s Molecular Foundry helped map the material’s nanoscale structural properties.

Evidence of phase transition

At ALS Beamline 4.0.2, the researchers used temperature-dependent x-ray absorption spectroscopy (XAS) and x-ray linear dichroism (XLD) studies to probe the structural evolution between the ferroelectric and antiferroelectric phases in the HZH. The results established the underlying microscopic origins of the negative capacitance and helped identify an antiferroelectric–ferroelectric transition near room temperature, suggesting a delicate balance between these competing phases that helps stabilize negative capacitance. Since complementary electrical measurements could not directly probe the 2 nm thick HZH film, the XAS data provided the best evidence of the underlying ferroic phase transition.

Looking forward, the researchers hope to demonstrate negative capacitance in this system down to a thickness of 1 nm, in line with future transistor architectures. From a materials design perspective, this work establishes that negative capacitance can originate from competing ferroelectric–antiferroelectric order, expanding the ferroic phase space for further negative capacitance explorations.

Contact: Suraj Cheema

Researchers: S.S. Cheema, N. Shanker, L.-C. Wang, C.-H. Hsu, S.-L. Hsu, Y.-H. Liao, W. Li, J.-H. Bae, S.K. Volkman, D. Kwon, Y. Rho, C.P. Grigoropoulos, and C. Hu (Univ. of California, Berkeley); M. San Jose, J. Gomez, W. Chakraborty, P. Fay, and S. Datta (Univ. of Notre Dame); G. Pinelli, R. Rastogi, D. Pipitone, C. Stull, M. Cook, B. Tyrrell, and M. Mohamed (Massachusetts Institute of Technology); V.A. Stoica (Pennsylvania State Univ.); Z. Zhang and J.W. Freeland (Argonne National Laboratory); C.J. Tassone and A. Mehta (SLAC National Accelerator Laboratory); G. Saheli and D. Thompson (Applied Materials, Inc.); D.I. Suh and W.-T. Koo (SK hynix, Korea); K.-J. Nam, D.J. Jung, W.-B. Song, S. Nam, and J. Heo (Samsung Electronics, Korea); C.-H. Lin (Intel Corporation); N. Parihar, and S. Mahapatra (Indian Institute of Technology); P. Shafer (ALS); J. Ciston (Berkeley Lab); and R. Ramesh and S. Salahuddin (Univ. of California, Berkeley, and Berkeley Lab).

Funding: Berkeley Center for Negative Capacitance Transistors, U.S. Department of Defense, University of California Multicampus Research Programs and Initiatives project, and the U.S. Department of Energy (DOE), Office of Basic Energy Sciences (BES), Materials Sciences and Engineering Division, Microelectronics Co-Design program. Operation of the ALS, APS, SSRL and Foundry is supported by DOE BES, Office of Science, Basic Energy Sciences program.

Publication: S.S. Cheema, N. Shanker, L.-C. Wang, C.-H. Hsu, S.-L. Hsu, Y.-H. Liao, M. San Jose, J. Gomez, W. Chakraborty, W. Li, J.-H. Bae, S. Volkman, D. Kwon, Y. Rho, G. Pinelli, R. Rastogi, D. Pipitone, C. Stull, M. Cook, B. Tyrrell, V.A. Stoica, Z. Zhang, J.W. Freeland, C.J. Tassone, A. Mehta, G. Saheli, D. Thompson, D.I. Suh, W.-T. Koo, K.-J. Nam, D.J. Jung, W.-B. Song, C.-H. Lin, S. Nam, J. Heo, N. Parihar, C.P. Grigoropoulos, P. Shafer, P. Fay, R. Ramesh, S. Mahapatra, J. Ciston, S. Datta, M. Mohamed, C. Hu, and S. Salahuddin, “Ultrathin ferroic HfO2-ZrO2 superlattice gate stack for advanced transistors,” Nature 604, 65 (2022), doi:10.1038/s41586-022-04425-6.

ALS SCIENCE HIGHLIGHT #469